Encounter Conformal Low Power enables designers to create power intent then verify and debug multimillion-gate designs optimized for low power without simulating test vectors. The intent of this design article is to provide a comprehensive tutorial on both the value of and the how to in using a hierarchical low-power design methodology.

Low Power Design Techniques Design Methodology And Tools Edn

Design Implementation Floorplan and power grids.

. Konform AR Acrylic Conformal Coating is easy to use offers great protective properties and is both IPC-CC-830B and UL certified. There are various EDA tools for performing LEC such as Synopsys Formality and Cadence Conformal. This is simple due to the ease of changing the output angle of incident light.

You may have even worked with them in the past. Conformal low power enables designers to create power intent then verify and debug multi-million-gate designs without simulating test vectors. We call yˆ the point prediction and we call Γ005 the region prediction.

There is certainly work needed in the possible focal lengths but with some work the length could allow for simplistic power transfer. Harmonic radar systems provide an effective modality for tracking insect behavior. Low Power Design And Verification A Tutorial on Conformal Prediction Glenn Shafer GSHAFERRUTGERSEDU Department of Accounting and Information Systems Rutgers Business School 180 University Avenue Newark NJ 07102 USA Vladimir Vovk.

It starts with defining the architectural requirements then microarchitecture development followed by RTL design and functional verification. Formal verification-driven equivalence low-power and ECO solutions. 1 Check to make sure you have the following files with the correct size in.

Laptop processors are mostly idle. It supports advanced dynamic and static power synthesis optimizations such as clock gating and signal gating multi-Vt libraries and de-cloning and re-cloning of gated clocks during clock tree synthesis and optimization. To run the tutorial install the tarkit and execute the following steps.

Encounter Conformal ASIC EC CONFRML52 USR1 Encounter Test ET 304 ISR. SR provides good chemical resistance moisture and salt spray resistance and is very flexible. Different needs for different markets Server market.

After all the preliminary checks are completed the synthesis netlist with ECO SYN2 and original post-routed netlist PNR1 are provided to the Conformal tool. Setup Mode Mapping Mode and Compare Mode. If you didnt know Conformals very own AE team put together some cool training materials for their customers based on.

Conformal Low Power supports the. The RTL netlist nrdmappedv. Server processors are rarely idle.

The educational resource for. As designs continue to get more complicated in order to meet aggressive requirements for power performance area and time to market the formal verification of the designs continues to be a staple and must-have signoff metric to ensure silicon success. Typically Γ005 also contains the prediction yˆ.

Design Representation Accurately define and capture the low power design intent modes and constraints. Accurate power estimation and measurements Design. In the case of classification.

By Kenneth Chang Core Comp AE. Hierarchical methods for power intent specification. This low power reference flow solution has been validated as being compatible with IBM and Chartered for their.

Reduce power in C2C3 power states. Processor design for Power Efficiency. Designing a chip is a complex process.

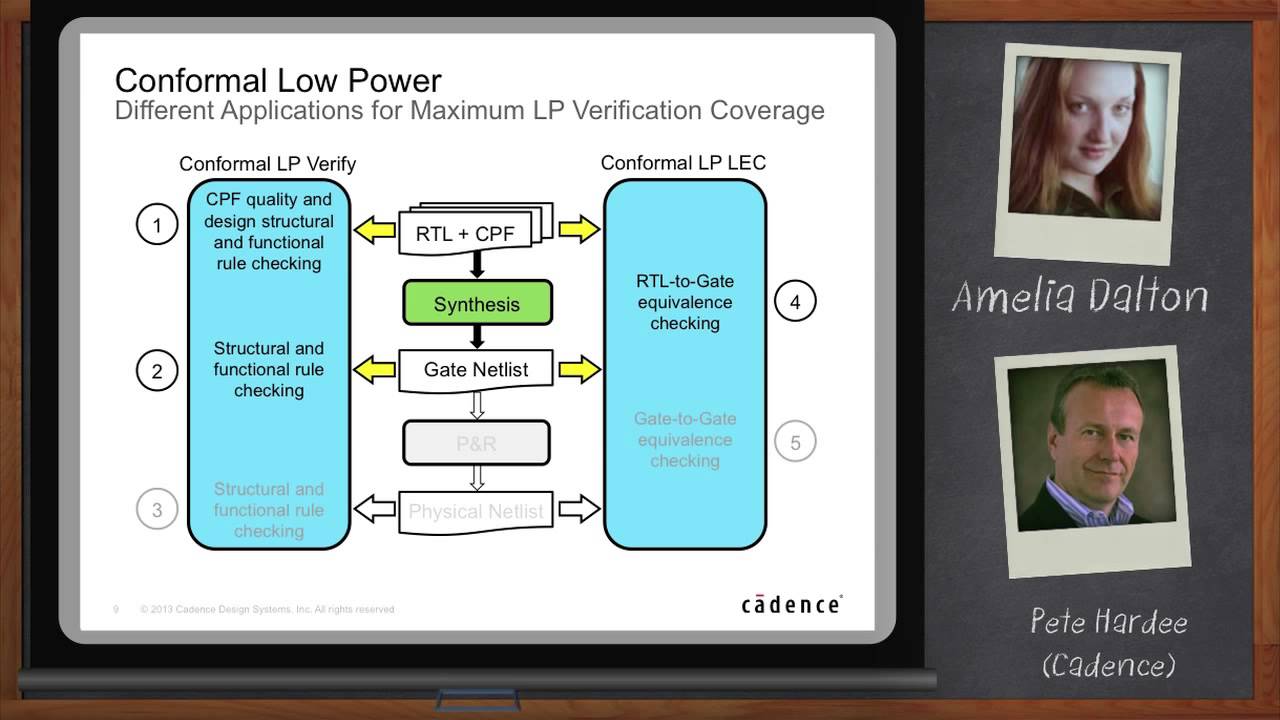

It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use. Common constraints for all tools Synthesis APR timing DFT Design analysis tools with single power constraints. The kit includes overviews tutorials with demo design instructions are provided on how to set up uthe ser environment and provides introductions for the advanced features of Conformal Low.

Logic Design Blogs. Logical Equivalence Check flow diagram. Conformal low power enables designers to create power intent then verify and debug multi-million-gate designs without simulating test vectors.

In the case of regression where y is a number Γ005 is typically an interval around yˆ. SHAFER AND VOVK regiona set Γ005 that contains y with probability at least 95. Cadence customers can learn more in a Rapid Adoption Kit RAK titled Conformal Low Power and RTL Compiler.

We are considering Conformal tool as a reference for the purpose of explaining the importance of LEC. Identify features of the Conformal Low-Power software 2. It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use.

Encounter Conformal Low Power RTL and its associated power intent. The file cellsv is identical to the verilog simulation files in the OSU cell library except for the DFFSR cells which required a small modification to work with Conformal. Access Free Conformal Lec User Manual Conformal Lec User Manual Introducing Conformal Smart LEC Introduction to conformal field theory Lecture 1 Understanding Logic Equivalence C.

It combines low-power structural and functional checks with world-class equivalence checking to provide superior performance capacity and ease of use. The following files are used in this tutorial. The gate level netlist cellsv.

Increase MIPSWatt in Power State C0 ACPI. This letter presents a harmonic radar system proposed to track the migration of the Emerald Ash Borer EAB. Then the design is synthesized to obtain a netlist which is handed to the back-end team to perform.

The article first shows how to express power intent top-down in a hierarchical design which allows the designer to set. Any bug found at this stage leads to an ECO which can be expensive. Low Power Verification for Advanced Users.

Silicone Resin SR Silicone conformal coating provides excellent protection in a very wide temperature range. A primer on logical equivalence checking LEC using Conformal. Primitive cells lecdo.

The system offers a unique combination of portability low power and small tag design. It is comprised of a compact radar unit and a passive RF tag for mounting on the insect. Get Free Conformal Lec User Manual Conformal Lec User Manual Introducing Conformal Smart LEC Introduction to conformal field theory Lecture 1 Understanding Logic Equivalence Chec.

Verification of the power intent of the design is captured and verified by Conformal Low Power CLP which requires a netlist even better a power connected netlist. The learning center for future and novice engineers electronics-tutorialsws. More information on LEC and its flow can be found in the first article of this series titled A primer on logical equivalence checking LEC using Conformal.

LEC comprises of three steps as shown below. There is already wireless power but these optical metasurfaces would make directing and focusing power a breeze. Team FED 22 Jun 2009.

Cadence Low Power Solution Rtl To Gdsii Low Power Design Cadence Youtube

Low Power Design And Verification

Low Power Design And Verification

Power Aware Verification Methodology Cadence

Low Power Design And Verification

Low Power Design Techniques Design Methodology And Tools Edn

Low Power Design Techniques Design Methodology And Tools Edn

0 comments

Post a Comment